The EP4CE30F23C7N is a popular FPGA (Field-Programmable Gate Array) used in a wide range of applications from consumer electronics to industrial devices. However, like any complex hardware, issues can arise during operation. This article offers a deep dive into common troubleshooting techniques and practical solutions to address potential problems with the EP4CE30F23C7N.

EP4CE30F23C7N, FPGA troubleshooting, FPGA solutions, common FPGA issues, troubleshooting EP4CE30F23C7N, FPGA error resolution, FPGA hardware problems

Understanding Common Problems with EP4CE30F23C7N and Initial Troubleshooting Steps

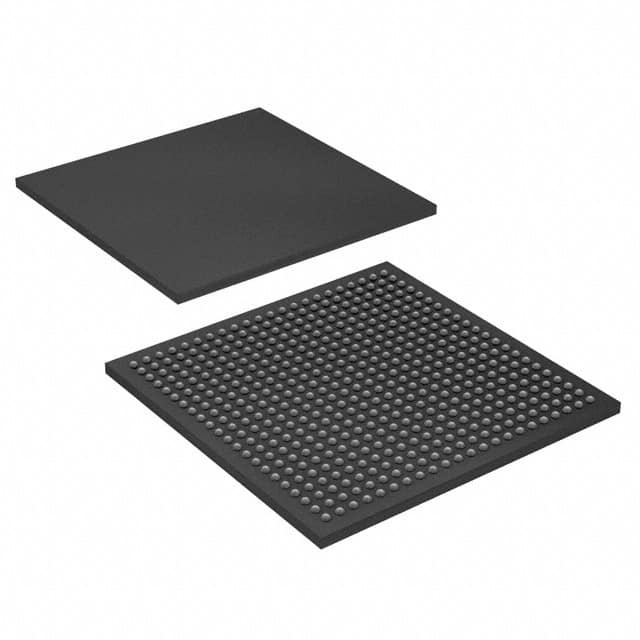

The EP4CE30F23C7N, a member of Altera's Cyclone IV series of FPGAs, is a versatile and Power ful device commonly used in applications like signal processing, embedded systems, and Communication systems. However, as with all electronic components, issues may arise that can hinder the performance of the FPGA. Understanding the potential problems and knowing how to troubleshoot them is essential for ensuring reliable operation and optimal performance.

1. Power Supply Issues

Problem: One of the most common issues faced with FPGAs, including the EP4CE30F23C7N, is power supply problems. The FPGA requires a stable and adequate power supply to function correctly. Variations in voltage or power interruptions can cause the device to behave unpredictably, leading to partial or total failure.

Solution:

Check Power Source: Start by verifying that the power supply is rated correctly for the EP4CE30F23C7N. The typical voltage for this FPGA is 3.3V, and any deviation from this could lead to instability or failure.

Measure Voltage Stability: Use a multimeter to measure the voltage at the FPGA’s power pins. It should stay within the recommended range (typically ±10%). If there's a noticeable fluctuation or drop, consider upgrading your power supply or using a voltage regulator.

Check for Grounding Issues: Ensure proper grounding, as grounding issues can lead to erratic behavior or even permanent damage to the device.

2. Configuration Problems

Problem: Configuration issues are another major source of problems in FPGAs. The EP4CE30F23C7N is often used in systems where the configuration data is loaded from external Memory (like a flash ROM). If the configuration file is corrupted, or the FPGA fails to load the configuration correctly, the device may not function as expected.

Solution:

Check Configuration File: Start by verifying that the bitstream file is correctly generated and valid. You can use the Quartus Prime software to check for any issues in the compilation process.

Test with a Known Good Configuration: If you suspect the configuration file might be corrupted, try loading a known good configuration to see if the problem persists.

Re-flash the FPGA: If the configuration file seems fine, attempt to re-flash the FPGA using a programmer or JTAG interface . Ensure the programming tool is set up correctly and that the programming process completes without errors.

3. Signal Integrity Problems

Problem: The EP4CE30F23C7N supports high-speed digital I/O, and signal integrity issues can arise when high-frequency signals are transmitted across long traces or with poor grounding. These issues can result in data corruption, Timing errors, or communication failures.

Solution:

Reduce Trace Lengths: In high-speed designs, minimizing the trace lengths of high-frequency signals is critical to ensuring signal integrity. Ensure that your PCB layout keeps critical signals short and as direct as possible.

Use Proper Termination: For high-speed signals, make sure to use proper impedance matching and termination techniques to minimize reflections and signal degradation.

Inspect for Noise: Noise can affect signal integrity, so check for sources of electromagnetic interference ( EMI ) in the design. Using ground planes and shielding can help mitigate this problem.

4. JTAG Communication Issues

Problem: JTAG (Joint Test Action Group) is a critical interface used for debugging and programming FPGAs like the EP4CE30F23C7N. Communication issues can arise if the JTAG connection is not properly established, which can prevent programming or debugging the FPGA.

Solution:

Check Cable Connections: The first step is to verify that the JTAG cable is securely connected to both the FPGA and the programming tool. Loose connections can often cause communication errors.

Verify JTAG Settings: Make sure that the correct JTAG settings are selected in the Quartus Prime software or any other software you're using. Double-check the chain settings to ensure that the FPGA is recognized correctly.

Test JTAG Interface: If communication is still not possible, test the JTAG interface on a different board or with a different FPGA to isolate whether the issue is with the EP4CE30F23C7N itself or the JTAG programming setup.

Advanced Troubleshooting for EP4CE30F23C7N and Solutions to Persistent Issues

When troubleshooting more advanced issues with the EP4CE30F23C7N FPGA, it’s essential to dive deeper into the FPGA’s architecture and surrounding systems. In this section, we’ll explore more complex troubleshooting scenarios and provide solutions to resolve persistent problems.

5. Clock Signal Issues

Problem: The EP4CE30F23C7N FPGA relies on external clock sources for proper operation. Clock signal issues, such as jitter, instability, or incorrect frequency, can lead to timing violations, causing the FPGA to behave unpredictably or fail to execute certain tasks.

Solution:

Verify Clock Source: Ensure that the external clock source is stable and provides the correct frequency. Use an oscilloscope to check the integrity of the clock signal at the input to the FPGA.

Check PLL Configuration: If your design uses a Phase-Locked Loop (PLL) to generate internal clock signals, make sure the PLL is configured correctly. Incorrect settings can lead to unstable clock outputs.

Look for Clock Skew: In multi-clock domain designs, clock skew can cause timing issues. Review the clock tree in your design and consider using clock domain crossing techniques, such as FIFOs or synchronizers, to avoid data corruption.

6. Temperature-Related Problems

Problem: The EP4CE30F23C7N is designed to operate within a specified temperature range. If the temperature exceeds this range, the FPGA may experience thermal-related failures, including loss of functionality, errors, or even permanent damage.

Solution:

Check Operating Environment: Verify that the FPGA is operating within the recommended temperature range (typically 0°C to 85°C). Ensure the system is not in a location where it could overheat.

Improve Cooling: If the FPGA is overheating, consider improving the cooling system by adding heat sinks or fans to dissipate heat more effectively.

Monitor Temperature: Some FPGAs have built-in temperature sensors that can provide real-time temperature readings. Use these sensors to monitor the operating temperature and ensure it stays within safe limits.

7. Design Issues: Timing Violations and Resource Overuse

Problem: Timing violations and resource overuse are often the result of poor FPGA design. If your design is too complex or has critical timing paths that are too tight, the FPGA may fail to meet the necessary setup and hold requirements, leading to errors or incorrect operation.

Solution:

Check Timing Reports: Use the timing analysis tools in Quartus Prime or your preferred design software to check for timing violations. Review the setup and hold reports to identify paths that are not meeting the timing constraints.

Optimize Design: If your design exceeds the FPGA’s available resources or performance capabilities, consider optimizing the design. This may involve simplifying logic, using more efficient algorithms, or reducing the number of parallel operations to reduce resource demand.

Use On-chip Resources Efficiently: The EP4CE30F23C7N has many on-chip resources, including memory blocks and DSP slices. Make sure your design efficiently uses these resources to reduce pressure on the FPGA’s logic fabric.

8. Memory and I/O Interface Failures

Problem: Memory and I/O failures are not uncommon in FPGA designs. These failures can occur due to issues with external memory devices, improper interface configurations, or timing mismatches.

Solution:

Verify Memory Interfaces: Check the interface between the FPGA and any external memory module s (e.g., SRAM, DDR). Ensure that the memory is correctly initialized and configured according to the FPGA’s requirements.

Check Pin Assignments: Ensure that the I/O pins used for memory or peripheral interfaces are correctly assigned in your design. Pin misconfigurations can cause communication failures or incorrect data transfer.

Analyze Timing for I/O: Use the timing analyzer to ensure that the setup and hold times for I/O signals are being met. For high-speed interfaces like DDR, consider using memory controllers or IP cores that handle timing requirements more effectively.

In conclusion, the EP4CE30F23C7N FPGA is a powerful and reliable component for many applications. However, as with any advanced hardware, issues can arise during its deployment. By following the troubleshooting steps outlined above and using appropriate diagnostic tools, you can identify and resolve common problems, ensuring that the FPGA operates efficiently and effectively.

If you are looking for more information on commonly used Electronic Components Models or about Electronic Components Product Catalog datasheets, compile all purchasing and CAD information into one place.

Partnering with an electronic components supplier sets your team up for success, ensuring the design, production, and procurement processes are quality and error-free.